技術解説 ブレーキ回路の設計と部品選定

ブラシレスモータドライバの設計事例

(回路ブロック編)

ブレーキ回路の設計と部品選定

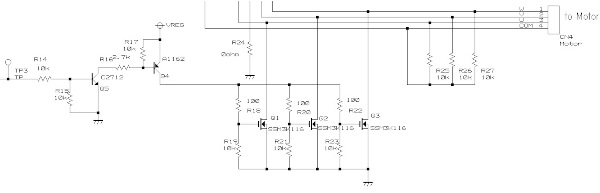

設計したショートブレーキ回路ブロックのschematic回路図を示します。

回路図

構成部品の選定

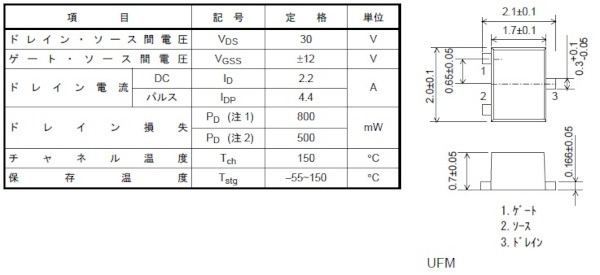

●電流短絡用FETトランジスタ(N-ch):Q1、Q2、Q3

できるだけ小型で安価、パフォーマンスの良いFETを選択しました。低いバイアス電圧(VGS=2.5V)で約0.1Ω級の低オン抵抗です。

2mm×1.7mmの小型SMDパッケージですが、例えば、1Aの電流を流しても1A×0.1Ω×1A ≒ 0.1W の熱損失しかありません。

- ・東芝製 MOSFET SSM3K116TU (UFM 2mm×1.7mm)

- ・パワーマネジメントスイッチ、高速スイッチング用途

- ・VGS=2.5V 駆動

- ・オン抵抗が低い : Ron = 135mΩ (max) (@VGS = 2.5V) Ron = 100mΩ (max) (@VGS = 4.5V)

(出展:東芝社SSK116TUデータシート)

●FET駆動用バッファ回路:

NPN Tr.とPNP Tr.のダーリントン接続でマイコンからの5V振幅信号をパワー増幅するバッファで3個のFETを駆動する構成です。

(1)前段Tr.:Q5 東芝製2SC2712 (SOT23)

汎用品で市場流通も多い安価なNPN Tr.です。

- <特長>

- ・高耐圧: VCEO = 50 V

- ・コレクタ電流が大きい: IC = 150 mA (最大)

- ・電流増幅率が高い : hFE = 70~700

- ・低雑音 : NF = 1dB (標準), 10dB (最大)

- ・2SA1162 とコンプリメンタリ

(2)後段Tr.:Q4 東芝製2SA1162 (SOT23)

汎用品で市場流通も多い安価なPNP Tr.です。2SC2712とコンプリメンタで、良く対に使われます。

- <特長>

- ・高耐圧 : VCEO = ?50V

- ・コレクタ電流が大きい: IC = ?150 mA (最大)

- ・電流増幅率が高い : hFE = 70~400

- ・低雑音 : NF = 1dB (標準), 10dB (最大)

この(1)と(2)の2個のトランジスタをダーリントン接続しており、電流増幅率は400以上ありますのでMCUの出力ポートの電流能力が0.5mAだとしても、ダーリントンバッファは、200mAの駆動能力を確保しており、FET3個分を駆動するには十分です。

●抵抗:R14,R15,R16,R17,R18,R19,R20,R21,R22,R23(0402)

特に大きな電流は流さない箇所の抵抗なので熱損失は極微です。よって、基板小型化のため、全て0402サイズの抵抗を使用しています。